DUXERIT coegi chip introductio

cum celeri progressione industriae electronicarum automotivarum, altae densitatis DUCTUS agitatoris astularum cum amplitudine intentionis inputationis late adhibitae sunt in lucendo autocineto, incluso exteriori ante et postico illuminando, interiori illuminando et backlighting ostentationem.

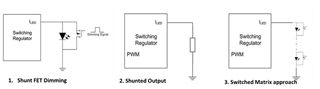

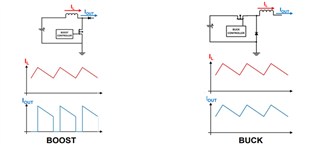

DUCTUS agitator chippis potest dividi in obscurationem analogam et PWM obscuratione secundum methodum obscurandi.Analoga obscuratio est relative simplex, PWM obscuratio est complexus respective, sed range obscurantia linearis maior est quam analogon obscuratio.DUXERIT agitator chip ut genus virtutis administratione chip, topologia eius maxime Buck et Boost.hircum circumiens output current continuum ita ut eius output venae laniatus minor sit, minore output facultatem requirat, magis conducit ad densitatem circuli altam potentiam consequendam.

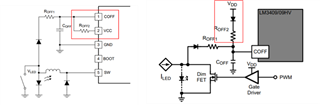

Figura I Output Current boost nobis Buck

Figura I Output Current boost nobis Buck

Communes modi moderatoris ductus astulae sunt modus current (CM), COFT (moderatus ON-tempus) modus, COFT & PCM (cacumen modus current) modus.Comparatus ad modum hodierni temperantiae, COFT modus moderandi ansam emendam non requirit, quae ad densitatem potentiam meliorandam confert, dum responsionem dynamicam citius habens.

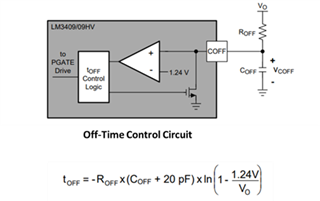

Dissimiles aliae ditionis modi, COFT moderandi modum chip habet separatum COFF paxillus ad temporis occasum.Articulus hic figuram et cautiones inducit ad ambitum externum COFF innixum in forma typica COFT continentis Buck DUXERIT coegi chip.

Configuratio fundamentalis COFF et cautiones

Imperium COFT modus principium est quod cum inductor currenti pervenit ad gradum currentem, tubus superior se vertit et tubus inferior se vertit.Cum vicissitudine ad TOFF pervenerit, superior rursus fistula volvitur.Postquam tubus superior deflexit, per constantem tempus remanebit (tOFF).tOFF ab capacitore (COFF) et output voltage (Vo) ponitur in peripheria circuli.Hoc ostenditur in Figura 2. Quia ILED est arcte regulata, Vo fere constans erit per amplis intentionum intentionum et temperaturarum, inde in fere constanti tOFF, quae uti Vo computari potest.

Figura 2. off temporis imperium circuit et formula calculi TOFF

Figura 2. off temporis imperium circuit et formula calculi TOFF

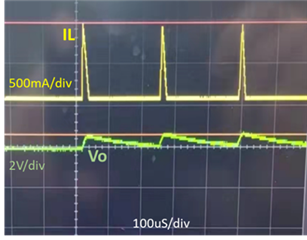

Animadvertendum est quod, cum delectis modum obscurationis vel ambitus obscurationis requirit breviata ratio, ambitus hoc tempore proprie non incipiet.Hoc tempore, inductor venae laniatus magnus fit, output voltatio valde gravis fit, multo minus quam intentione statuta.Cum haec defectio incidit, inductor currenti cum maximo temporis spatio laborabit.Solet maximum temporis spatium intra chip inclusum attingit 200us~300us.In hoc tempore inductor currentis et output voltage videtur singultum modum inire et normaliter output non potest.Figura 3 ostendit abnormes fluctus inductoris currentis et output intentionis TPS92515-Q1 quando resistor fugitivorum pro onere adhibetur.

Instar 4 circuitus tria genera ostendit, qui praedicta vitia faciant.Cum shunt FET ad obscurationem adhibetur, resistor fugitivorum oneris delectus est, et onus ducitur mutatio matricis circuit, omnes breves sunt output voltage et ne normales satus-usque.

Figura III TPS92515-Q1 Inductor Current et Output intentione (Resistor Lond output Short Grand)

Figura III TPS92515-Q1 Inductor Current et Output intentione (Resistor Lond output Short Grand)

Figure 4. Circuitus qui potest facere output bracis

Ad hoc vitandum, etiam cum breviatur output, addito intentione adhuc opus est ut COFF insimulet.Copia parallela quam VCC/VDD adhiberi potest ut capacitores COFF obicit, tempus stabile conservat et tremor constantem servat.Customers resistor ROFF2 inter VCC/VDD et COFF reservare possunt cum ambitum designant, ut in Figura V ostenditur, quo postea opus debugging faciliorem reddat.Eodem tempore, TI chip datasheet plerumque dat formulam calculi specificam ROFF2 secundum internum ambitum domatis ad electionem resistoris emptoris faciliorem.

Figure 5. SHUNT FET EXTERNIS ROFF2 Improvement Circuit

Figure 5. SHUNT FET EXTERNIS ROFF2 Improvement Circuit

Cum breve spatium outputium culpae TPS92515-Q1 in Figura 3 exemplum sumens, methodus mutata in Figura 5 adhibetur addere ROFF2 inter VCC et COFF ut COFF insimularet.

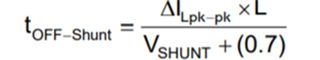

Discriptis ROFF2 duos gradus processus est.Primus gradus shutdown temporis (tOFF-SHunt) requisitum computare cum resistor fugitivorum pro output adhibetur, ubi VSHUNT est output intentionis cum fugitivus resistor pro onere ponitur.

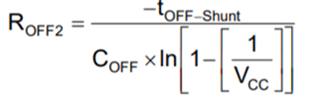

Secundus gradus est uti tOFF-SHunt computare ROFF2, quod est crimen a VCC ad COFF per ROFF2, ut sequitur.

Secundus gradus est uti tOFF-SHunt computare ROFF2, quod est crimen a VCC ad COFF per ROFF2, ut sequitur.

Ex calculo, elige convenientem valorem ROFF2 (50k Ohm) et iungo ROFF2 inter VCC et COFF in casu culpae in Figura 3, cum ambitus output normale est.Item nota quod ROFF2 multo maior debet esse quam ROFF1;si minor est, TPS92515-Q1 difficultates minimas vicissitudines experietur, quae provenient in incremento currenti et damnum fieri posse cum fabrica chip.

Ex calculo, elige convenientem valorem ROFF2 (50k Ohm) et iungo ROFF2 inter VCC et COFF in casu culpae in Figura 3, cum ambitus output normale est.Item nota quod ROFF2 multo maior debet esse quam ROFF1;si minor est, TPS92515-Q1 difficultates minimas vicissitudines experietur, quae provenient in incremento currenti et damnum fieri posse cum fabrica chip.

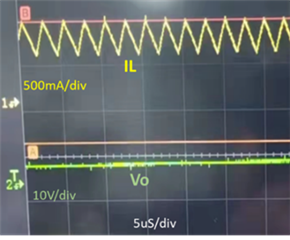

Figure 6. TPS92515-Q1 inductor currentis et output voltage (normalis additis ROFF2)

Figure 6. TPS92515-Q1 inductor currentis et output voltage (normalis additis ROFF2)

Post tempus: Feb-15-2022